tính chất của sản phẩm:

| LOẠI HÌNH | MÔ TẢ |

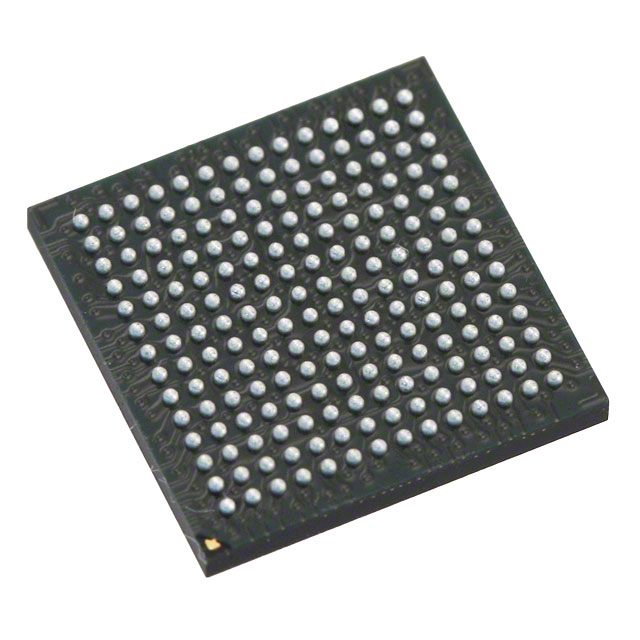

| thể loại | Mạch tích hợp (IC) Embedded - FPGA (Field Programmable Gate Array) |

| nhà chế tạo | AMD Xilinx |

| loạt | Spartan®-6 LX |

| Bưu kiện | cái mâm |

| trạng thái sản phẩm | trong kho |

| Số phòng thí nghiệm/câu lạc bộ | 300 |

| Số phần tử logic/đơn vị | 3840 |

| Tổng số bit RAM | 221184 |

| số lượng vào/ra | 106 |

| Điện áp - Powered | 1,14V ~ 1,26V |

| Loại cài đặt | Loại gắn bề mặt |

| Nhiệt độ hoạt động | 0°C ~ 85°C (TJ) |

| Gói / Bao vây | 196-TFBGA, CSBGA |

| Bao bì thiết bị nhà cung cấp | 196-CSPBGA (8x8) |

| Số sản phẩm cơ bản | XC6SLX4 |

báo lỗi

Phân loại Môi trường và Xuất khẩu:

| THUỘC TÍNH | MÔ TẢ |

| tình trạng RoHS | Tuân thủ thông số kỹ thuật ROHS3 |

| Mức độ nhạy cảm với độ ẩm (MSL) | 3 (168 giờ) |

| trạng thái ĐẠT | Sản phẩm KHÔNG ĐẠT ĐƯỢC |

| ECCN | EAR99 |

| HTSUS | 8542.39.0001 |

Ghi chú:

1. Ứng suất vượt quá những ứng suất được liệt kê trong Định mức tối đa tuyệt đối có thể gây hư hỏng vĩnh viễn cho thiết bị.Đây là những xếp hạng căng thẳng

và hoạt động chức năng của thiết bị ở những điều kiện này hoặc bất kỳ điều kiện nào khác ngoài những điều kiện được liệt kê trong Điều kiện hoạt động không được ngụ ý.

Tiếp xúc với các điều kiện Xếp hạng tối đa tuyệt đối trong thời gian dài có thể ảnh hưởng đến độ tin cậy của thiết bị.

2. Khi lập trình eFUSE thì VFS ≤ VCCAUX.Yêu cầu dòng điện lên đến 40 mA.Đối với chế độ đọc, VFS có thể nằm trong khoảng từ GND đến 3,45 V.

3. Giới hạn tối đa tuyệt đối I/O áp dụng cho tín hiệu DC và AC.Thời lượng vượt quá là tỷ lệ phần trăm của khoảng thời gian dữ liệu mà I/O bị căng thẳng

vượt quá 3,45V.

4. Để biết thao tác I/O, hãy tham khảo UG381: Hướng dẫn sử dụng tài nguyên Spartan-6 FPGA SelectIO.

5. Khoảng thời gian phần trăm vượt quá tối đa để đáp ứng tối đa 4,40V.

6. TSOL là nhiệt độ hàn tối đa cho thân linh kiện.Đối với hướng dẫn hàn và xem xét nhiệt,

xem UG385: Đặc điểm kỹ thuật sơ đồ và đóng gói FPGA Spartan-6.

Điều kiện hoạt động được đề xuất(1)

Biểu tượng Mô tả Min Typ Max Đơn vị

VCCI

Điện áp cung cấp bên trong so với GND

-3, -3N, -2 Hiệu suất tiêu chuẩn(2)

1,14 1,2 1,26V

-3, -2 Hiệu suất mở rộng(2)

1,2 1,23 1,26V

-1L Hiệu suất tiêu chuẩn(2)

0,95 1,0 1,05 V

VCCAUX(3)(4) Điện áp nguồn phụ so với GND

VCCAUX = 2.5V(5)

2.375 2.5 2.625 V

VCCAUX = 3,3V 3,15 3,3 3,45V

VCCO(6)(7)(8) Điện áp nguồn đầu ra so với GND 1,1 – 3,45 V

số VIN

Điện áp đầu vào so với GND

Tất cả I/O

tiêu chuẩn

(ngoại trừ PCI)

Nhiệt độ thương mại (C) –0,5 – 4,0 V

Nhiệt độ công nghiệp (I) –0,5 – 3,95 V

Nhiệt độ mở rộng (Q) –0,5 – 3,95 V

Chuẩn I/O PCI(9)

–0,5 – VCCO + 0,5 V

IIN(10)

Dòng tối đa qua chân sử dụng chuẩn PCI I/O

khi phân cực thuận điốt kẹp.(9)

Thương mại (C) và

Nhiệt độ công nghiệp (I)

– – 10mA

Nhiệt độ mở rộng (Q) – – 7 mA

Dòng điện tối đa qua chân khi phân cực thuận điốt kẹp đất.– – 10mA

VBATT(11)

Điện áp pin so với GND, Tj = 0°C đến +85°C

(Chỉ dành cho LX75, LX75T, LX100, LX100T, LX150 và LX150T)

1,0 – 3,6V

Tj

Phạm vi hoạt động của nhiệt độ đường giao nhau

Phạm vi thương mại (C) 0 – 85 °C

Dải nhiệt độ công nghiệp (I) –40 – 100 °C

Phạm vi nhiệt độ mở rộng (Q) –40 – 125 °C

Ghi chú:

1. Tất cả các điện áp đều liên quan đến mặt đất.

2. Xem Hiệu suất giao diện cho Giao diện bộ nhớ trong Bảng 25. Phạm vi hiệu suất mở rộng được chỉ định cho các thiết kế không sử dụng

dải điện áp tiêu chuẩn VCCINT.Dải điện áp VCCINT tiêu chuẩn được sử dụng cho:

• Thiết kế không sử dụng MCB

• Thiết bị LX4

• Máy thuộc gói TQG144 hoặc CPG196

• Thiết bị có cấp tốc độ -3N

3. Độ sụt điện áp tối đa khuyến nghị cho VCCAUX là 10 mV/ms.

4. Trong quá trình cấu hình, nếu VCCO_2 là 1,8V thì VCCAUX phải là 2,5V.

5. Các thiết bị -1L yêu cầu VCCAUX = 2.5V khi sử dụng LVDS_25, LVDS_33, BLVDS_25, LVPECL_25, RSDS_25, RSDS_33, PPDS_25,

và tiêu chuẩn I/O PPDS_33 trên đầu vào.LVPECL_33 không được hỗ trợ trong các thiết bị -1L.

6. Dữ liệu cấu hình được giữ lại ngay cả khi VCCO giảm xuống 0V.

7. Bao gồm VCCO 1.2V, 1.5V, 1.8V, 2.5V và 3.3V.

8. Đối với hệ thống PCI, máy phát và máy thu phải có nguồn cung cấp chung cho VCCO.

9. Các thiết bị có cấp tốc độ -1L không hỗ trợ Xilinx PCI IP.

10. Tổng cộng không vượt quá 100 mA mỗi dãy.

11. Cần có VBATT để duy trì phím AES RAM (BBR) được hỗ trợ bằng pin khi không áp dụng VCCAUX.Khi VCCAUX được áp dụng, VBATT có thể được

không được kết nối.Khi BBR không được sử dụng, Xilinx khuyên bạn nên kết nối với VCCAUX hoặc GND.Tuy nhiên, VBATT có thể không được kết nối.